搜索

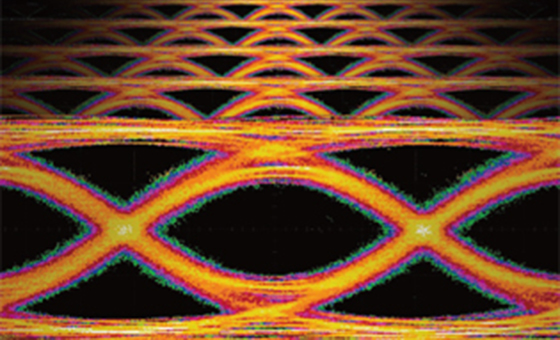

高速串行總線的信號完整性驗證一般來講,電子產(chǎn)品的設(shè)計都離不開以下幾個部分:電源、時鐘、復位信號、總線和接口,正是這些各個部分的信號連接著整個系統(tǒng),也是決定系統(tǒng)穩(wěn)定性的重要角色之一。系統(tǒng)的穩(wěn)定性和設(shè)計質(zhì)量的好壞,從信號本身的角度可以看出絲許端倪,其實這也就是信號完整性研究的內(nèi)容...

高速串行總線的信號完整性驗證一般來講,電子產(chǎn)品的設(shè)計都離不開以下幾個部分:電源、時鐘、復位信號、總線和接口,正是這些各個部分的信號連接著整個系統(tǒng),也是決定系統(tǒng)穩(wěn)定性的重要角色之一。系統(tǒng)的穩(wěn)定性和設(shè)計質(zhì)量的好壞,從信號本身的角度可以看出絲許端倪,其實這也就是信號完整性研究的內(nèi)容... 2014/09/22

2014/09/22 8283

8283 用串行RapidIO交換處理高速電路板設(shè)計的信號完整性信號完整性(SI)問題正成為數(shù)字硬件設(shè)計人員越來越關(guān)注的問題。由于無線基站、無線網(wǎng)絡(luò)控制器、有線網(wǎng)絡(luò)基礎(chǔ)架構(gòu)及軍用航空電子系統(tǒng)中數(shù)據(jù)速率帶寬增加,電路板的設(shè)計變得日益復雜...

用串行RapidIO交換處理高速電路板設(shè)計的信號完整性信號完整性(SI)問題正成為數(shù)字硬件設(shè)計人員越來越關(guān)注的問題。由于無線基站、無線網(wǎng)絡(luò)控制器、有線網(wǎng)絡(luò)基礎(chǔ)架構(gòu)及軍用航空電子系統(tǒng)中數(shù)據(jù)速率帶寬增加,電路板的設(shè)計變得日益復雜... 2014/09/16

2014/09/16 11487

11487 串行總線設(shè)計相關(guān)優(yōu)勢特點解析方案隨著目前對通信和計算機系統(tǒng)速度與帶寬的需求不斷上升,系統(tǒng)設(shè)計師正面臨著嚴峻的考驗。按時序進行測試的并行總線結(jié)構(gòu)已接近其能力的極限,總線寬度現(xiàn)達到 64位以上,致使電路布局異常復雜...

串行總線設(shè)計相關(guān)優(yōu)勢特點解析方案隨著目前對通信和計算機系統(tǒng)速度與帶寬的需求不斷上升,系統(tǒng)設(shè)計師正面臨著嚴峻的考驗。按時序進行測試的并行總線結(jié)構(gòu)已接近其能力的極限,總線寬度現(xiàn)達到 64位以上,致使電路布局異常復雜... 2014/09/16

2014/09/16 5292

5292