技術中心

減少無法加工的風險,解密生產制造,了解行業規范和術語,提升行業技能

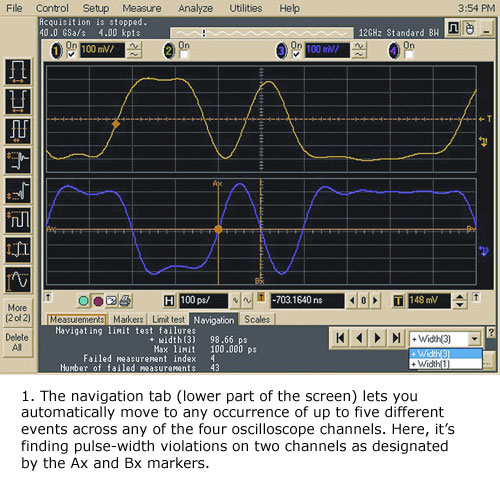

高速電路設計中信號完整性問題的快速定位在高速電路設計中,定位信號完整性問題的傳統方法是采用硬件觸發來隔離事件,和/或利用深度采集存儲技術捕獲事件,然后再尋找問題。隨著高性能電路系統的速度和復雜程度的不斷提高,用示波器定位信號完整性問題的局限性也在逐步凸顯...

高速電路設計中信號完整性問題的快速定位在高速電路設計中,定位信號完整性問題的傳統方法是采用硬件觸發來隔離事件,和/或利用深度采集存儲技術捕獲事件,然后再尋找問題。隨著高性能電路系統的速度和復雜程度的不斷提高,用示波器定位信號完整性問題的局限性也在逐步凸顯... 2014-09-12

2014-09-12 7299

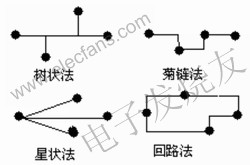

7299 高速電路設計中信號完整性分析本篇介紹了高速數字硬件電路設計中信號完整性在通常設計的影響。這包括特征阻抗控制、終端匹配、電源和地平面、信號布線和串擾等問題。掌握這些知識,對一個數字電路設計者而言,可以在電路設計的早期,就注意到潛在可能的信號完整性問題,還可以幫助設計則在設計中盡量避免信號完整性對設計性能的影

高速電路設計中信號完整性分析本篇介紹了高速數字硬件電路設計中信號完整性在通常設計的影響。這包括特征阻抗控制、終端匹配、電源和地平面、信號布線和串擾等問題。掌握這些知識,對一個數字電路設計者而言,可以在電路設計的早期,就注意到潛在可能的信號完整性問題,還可以幫助設計則在設計中盡量避免信號完整性對設計性能的影 2014-09-12

2014-09-12 6281

6281 VGA視頻分配器系統的信號完整性改善方法處理高速電子系統的信號完整性問題一直是比較難于處理的,特別是越來越多的芯片的工作頻率超過了100 MHz,信號的邊沿越來越陡(已達到ps級) ,這些高速器件性能的提高更增加了系統設計的難度。同時,高速系統的體積不斷減小使得PCB板的密度迅速提高。信號完整性問題已經成為新一代高速產品設計中越來越值得注意的問題

VGA視頻分配器系統的信號完整性改善方法處理高速電子系統的信號完整性問題一直是比較難于處理的,特別是越來越多的芯片的工作頻率超過了100 MHz,信號的邊沿越來越陡(已達到ps級) ,這些高速器件性能的提高更增加了系統設計的難度。同時,高速系統的體積不斷減小使得PCB板的密度迅速提高。信號完整性問題已經成為新一代高速產品設計中越來越值得注意的問題 2014-09-12

2014-09-12 7170

7170 利用IBIS模型研究信號完整性問題本文是關于在印刷電路板 (PCB) 開發階段使用數字輸入/輸出緩沖信息規范 (IBIS) 模擬模型的文章。本文將介紹如何使用一個 IBIS 模型來提取一些重要的變量,用于信號完整性計算和確定 PCB 設計解決方案

利用IBIS模型研究信號完整性問題本文是關于在印刷電路板 (PCB) 開發階段使用數字輸入/輸出緩沖信息規范 (IBIS) 模擬模型的文章。本文將介紹如何使用一個 IBIS 模型來提取一些重要的變量,用于信號完整性計算和確定 PCB 設計解決方案 2014-09-12

2014-09-12 5919

5919 3G網絡與PCB信號完整性問題3G網絡與PCB信號完整性問題

3G網絡與PCB信號完整性問題3G網絡與PCB信號完整性問題 2014-09-12

2014-09-12 5389

5389