技術中心

減少無法加工的風險,解密生產制造,了解行業規范和術語,提升行業技能

基于信號完整性分析的高速數字PCB的設計方法隨著集成電路輸出開關速度提高以及PCB板密度增加,信號完整性已經成為高速數字PCB設計必須關心的問題之一。元器件和PCB板的參數、元器件在PCB板上的布局、高速信號的布線等因素,都會引起信號完整性問題,導致系統工作不穩定,甚至完全不工作

基于信號完整性分析的高速數字PCB的設計方法隨著集成電路輸出開關速度提高以及PCB板密度增加,信號完整性已經成為高速數字PCB設計必須關心的問題之一。元器件和PCB板的參數、元器件在PCB板上的布局、高速信號的布線等因素,都會引起信號完整性問題,導致系統工作不穩定,甚至完全不工作 2014-09-12

2014-09-12 5525

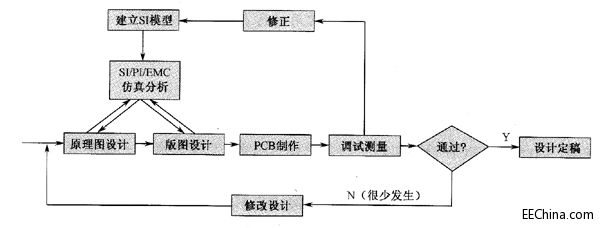

5525 基于信號完整性分析的PCB設計方法基于信號完整性分析的PCB設計流程如圖所示。

基于信號完整性分析的PCB設計方法基于信號完整性分析的PCB設計流程如圖所示。 2014-09-12

2014-09-12 5813

5813 關注復雜設計中的信號完整性在SoC設計中,信號之間的耦合作用會產生信號完整性問題,忽視信號完整性問題可能導致信號之間產生串擾,可靠性、可制造性和系統性能也會降低,本文介紹在ASIC芯片設計中解決信號完整性問題的方法

關注復雜設計中的信號完整性在SoC設計中,信號之間的耦合作用會產生信號完整性問題,忽視信號完整性問題可能導致信號之間產生串擾,可靠性、可制造性和系統性能也會降低,本文介紹在ASIC芯片設計中解決信號完整性問題的方法 2014-09-12

2014-09-12 5015

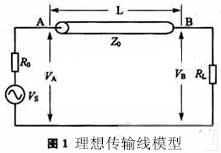

5015 高速數字系統中的信號完整性及實施方案現在的高速數字系統的時鐘頻率可能高達數百兆Hz,其快斜率瞬變和極高的工作頻率,以及很大的電路密集度,必將使得系統表現出與低速設計截然不同的行為,出現了信號完整性問題...

高速數字系統中的信號完整性及實施方案現在的高速數字系統的時鐘頻率可能高達數百兆Hz,其快斜率瞬變和極高的工作頻率,以及很大的電路密集度,必將使得系統表現出與低速設計截然不同的行為,出現了信號完整性問題... 2014-09-12

2014-09-12 8827

8827 高速數字電路的信號完整性與電磁兼容性設計從IC芯片的發展及封裝形式來看,芯片體積越來越小、引腳數越來越多;同時,由于近年來IC工藝的發展,使得其速度也越來越高。這就帶來了一個問題,即電子設計的體積減小導致電路的布局布線密度變大,而同時信號的頻率還在提高,從而使得如何處理高速信號問題成為一個設計能否成功的關鍵因素

高速數字電路的信號完整性與電磁兼容性設計從IC芯片的發展及封裝形式來看,芯片體積越來越小、引腳數越來越多;同時,由于近年來IC工藝的發展,使得其速度也越來越高。這就帶來了一個問題,即電子設計的體積減小導致電路的布局布線密度變大,而同時信號的頻率還在提高,從而使得如何處理高速信號問題成為一個設計能否成功的關鍵因素 2014-09-12

2014-09-12 8724

8724